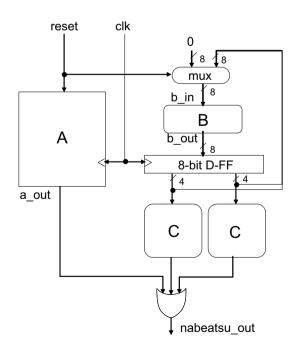

- 3. 図 1 に示す回路は,リセット (reset) 信号が 1 から 0 になってからのクロック (clk) 数が,3 の倍数か,16 進表記で 3 を含む数字になるときに 1 を,それ以外のときに 0 を出力する順序回路である (変形ナベアツ機械と呼ぶ).ただし,クロック数としては 255 (16 進表記で FF) までのみを考慮する.以下の問いに答えよ.

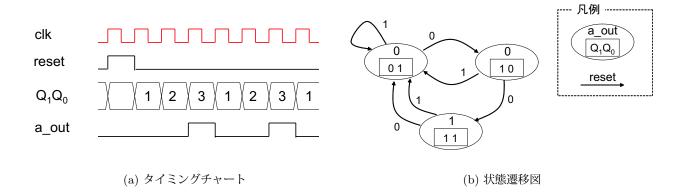

- (1) ブロック A は,リセット後のクロック数が 3 の倍数のときにのみ出力 a\_out が 1 となるような順序回路である.そのタイミングチャートおよび状態遷移図はそれぞれ図 2(a),図 2(b) の通りとする.この順序回路の状態遷移表を示せ.すなわち,現時刻の状態  $\{Q_1,Q_0\}$  と入力 reset の組に対する次時刻の状態  $\{Q_1^{\text{next}},Q_0^{\text{next}}\}$  と出力 a\_out の組を列挙した表をかけ.なお,冗長項 (don't care term) がある場合は \* で示すこと.

- (2) 問 (1) のとき, $Q_1^{

m next}$  および  $Q_0^{

m next}$  のそれぞれを  $Q_1$ , $Q_0$ ,reset の論理関数として,a\_out を  $Q_1$ , $Q_0$  の論理関数として表せ.(要訂正)

- (3) 問 (2) で求めた論理関数のそれぞれを , できるだけ簡単な積和型の論理式で表し , それに基づいて ブロック A の順序回路の回路図をかけ . AND, OR, NOT の各論理ゲートと , クロック同期型 D フリップフロップを使用してよい .

- (4) ブロック B は , 8 ビットの入力 b\_in を受け取り , それに 1 を加えた 8 ビット値 b\_out を出力する 組合せ回路である . 全加算器を 8 個用いてこの組合せ回路を構成せよ .

- (5) ブロック C は,8 ビットのクロック同期 D フリップフロップ (8-bit D-FF) の出力のうち上位 4 ビットと下位 4 ビットをそれぞれ受け取り,それが 16 進表記で 3 のときに 1 を,それ以外のとき 0 を出力する組合せ回路である.その入出力関係を表す真理値表をかき,回路図を示せ.AND, OR,NOT の各論理ゲートを使用してよい.

- (6) 以上で設計した変形ナベアツ機械をもとに「16 進表記で3 を含む数字になるとき」という条件を「10 進表記で3 を含む数字になるとき」という条件に置き換えた純粋ナベアツ機械を設計したい. どのような改変をすればよいか述べよ.ただし,クロック数としては99 までのみを考慮する.なお,具体的な回路設計を示す必要はないが,そのような努力をした場合は評点上考慮する.

図 1: 変形ナベアツ機械

図 2: ブロック A のタイミングチャートと状態遷移図